1. Tujuan [kembali]

- Dapat mengetahui pengertian dari Multiple BJT Networks

- Mampu memahami dan manganalisa apa itu transistor

- Dapat mengatahui rumus-rumus yang digunakan dalam Multiple BJT Network

- Mampu memahami rangkaian-rangkaian yang dibuat pada aplikasi proteus

2. Komponen [kembali]

a. Transistor, sebuah komponen elektronika yang digunakan untuk penguat, sebagai sirkuit pemutus,

sebagai penyambung, sebagai stabilitas tegangan, dan modulasi sinyal.

b. Kapasitor, adalah komponen elektronika yang berfungsi menyimpan muatan listrik dalam jangka

waktu tertentu.

c. Resistor, merupakan suatu komponen elektronik yang memiliki nilai resistansi atau hambatan

tertentu yang berfungsi untuk membatasi dan mengatur tegangan dan arus listrik.

d. Ground, titik yang dianggap sebagai titik kembalinya arus listrik arus searah atau titik kembalinya

sinyal bolak balik atau titik patokan (referensi) dari berbagai titik tegangan yang berfungsi sebagai

pengaman ketika terjadi kebocoran arus listrik.

e. Vsine, sebagai sumber Tegangan AC

3. Ringkasan [kembali]

Jaringan BJT yang diperkenalkan sejauh ini hanya berupa konfigurasi satu tahap. Bagian ini akan mencakup beberapa jaringan paling populer yang menggunakan banyak transistor. Itu akan mendemonstrasikan bagaimana metode yang diperkenalkan sejauh ini dalam bab ini dapat diterapkan pada jaringan dengan sejumlah komponen.

Kopling R–C pada Gambar 4.64 mungkin yang paling umum. Output kolektor dari satu tahap diumpankan langsung ke dasar tahap berikutnya menggunakan kapasitor kopling C C . Kapasitor dipilih untuk memastikan bahwa itu akan memblokir dc di antara tahapan dan bertindak seperti korsleting setiap sinyal ac. Jaringan pada Gambar 4.64memiliki dua tahap pembagi tegangan, tetapi kopling yang sama dapat digunakan antara kombinasi jaringan seperti fixed-bias atau emitter-follower konfigurasi. Mengganti setara sirkuit terbuka untuk C C dan kapasitor lainnya dari jaringan akan menghasilkan dua pengaturan bias yang ditunjukkan pada Gambar 4.65. Metode analisis diperkenalkan dalam bab ini kemudian dapat diterapkan ke setiap tahap secara terpisah karena satu tahap tidak mempengaruhi yang lain. Tentu saja, suplai 20 V dc harus diterapkan pada setiap komponen yang diisolasi.

Konfigurasi Darlington pada Gambar 4.66 mengumpankan output dari satu tahap langsung ke input dari tahap berikutnya. Karena output dari Gambar 4.66 diambil langsung dari terminal emitor, Anda akan menemukan di bab berikutnya bahwa gain ac sangat dekat dengan 1 tetapi impedansi inputnya sangat tinggi, membuatnya menarik untuk digunakan pada amplifier yang beroperasi mati sumber yang memiliki resistansi internal yang relatif tinggi. Jika resistor beban ditambahkan ke kaki kolektor dan output diambil dari terminal kolektor, konfigurasi akan memberikan keuntungan yang sangat tinggi.

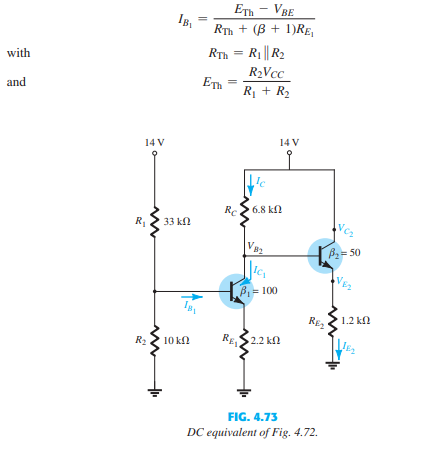

Untuk analisis dc pada Gambar 4.67 dengan asumsi beta b1 untuk transistor pertama dan b2 untuk transistor kedua, arus basis untuk transistor kedua adalah:

dan arus emitor untuk transistor kedua adalah:

asumsikan Beta = 1 untuk setiap transistor, kita akan menemukan jaringan Beta untuk konfigurasinya adalah:

yang membandingkan langsung dengan penguat satu tahap yang memiliki penguatan sebesar beta D Menerapkan analisis yang mirip dengan Bagian 4.4 sebelumnya akan menghasilkan persamaan berikut

untuk arus basis:

Konfigurasi Cascode pada Gambar 4.68 mengikat kolektor dari satu transistor ke emitor dari yang lain. Intinya ini adalah jaringan pembagi tegangan dengan konfigurasi common-base di pengumpul. Hasilnya adalah jaringan dengan gain tinggi dan kapasitansi Miller yang berkurang—atopik yang akan diperiksa di Bagian 9.9.

Analisis dc dimulai dengan mengasumsikan arus melalui resistor bias R1 , R2 , dan R3 dari Gambar 4.69 jauh lebih besar dari arus basis masing-masing transistor. Itu adalah,

Hasilnya tegangan pada basis transistor Q1 ditentukan secara sederhana oleh penerapan aturan pembagi tegangan:

Tegangan di dasar transistor Q2 ditemukan dengan cara yang sama:

Tegangan emitor kemudian ditentukan oleh: dengan arus emitor dan kolektor ditentukan oleh:

Konfigurasi multitahap berikutnya yang akan diperkenalkan adalah Pasangan Umpan Balik pada Gambar 4.70, yang menggunakan transistor npn dan pnp. Hasilnya adalah konfigurasi yang menyediakan gain tinggi dengan peningkatan stabilitas.

Versi dc dengan semua arus berlabel muncul di Gambar 4.71.

Arus basis:

Menerapkan hukum tegangan Kirchhoff turun dari sumber ke tanah akan menghasilkan:

Tegangan kolektor VC2 = VE1

adalah

Konfigurasi multistage terakhir yang diperkenalkan adalah penguat Direct Coupled seperti yang terlihat pada Contoh 4.26. Perhatikan tidak adanya kopling kapasitor untuk mengisolasi dc level dari setiap tahapan. Level dc dalam satu tahap akan secara langsung mempengaruhi level dc di tahap selanjutnya. Manfaatnya adalah kapasitor kopling biasanya membatasi frekuensi rendah respon dari penguat. Tanpa kopling kapasitor, amplifier dapat memperkuat sinyal frekuensi sangat rendah—sebenarnya turun ke dc. Kerugiannya adalah variasi level dc karena berbagai alasan dalam satu tahap dapat mempengaruhi tingkat dc di tahap berikutnya

penguat.

4. Example [kembali]

Tentukan level dc untuk arus dan tegangan dari direct coupled penguat dari Gambar 4.72. Perhatikan bahwa ini adalah konfigurasi bias pembagi tegangan yang diikuti oleh sebuah konfigurasi kolektor umum; salah satu yang sangat baik dalam kasus di mana impedansi masukan tahap berikutnya cukup rendah. Penguat common-collector bertindak seperti buffer antar tahapan.

Solusi: Persamaan dc dari Gambar 4.72 muncul sebagai Gambar 4.73 . Perhatikan bahwa beban dan sumber tidak lagi menjadi bagian dari gambar. Untuk konfigurasi pembagi tegangan, persamaan berikut untuk arus basis dikembangkan di Bagian 4.5.

Pada Gambar 4.73 kita menemukan bahwa:5. Problem [kembali]

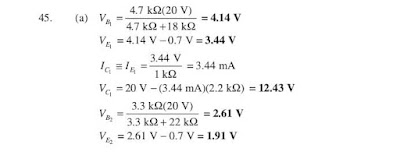

1. Untuk penguat R–C-coupled pada Gambar 4.141 tentukan :

a. Tegangan VB, VC, dan VE untuk setiap transistor.

b. Arus IB, IC, dan IE untuk masing-masing transistor.

Jawab:

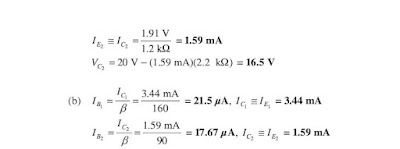

2. Untuk penguat Darlington pada Gambar 4.142 tentukan :

a. Tingkat bD

b. Arus basis masing-masing transistor

c. Arus kolektor masing-masing transistor

d. Tegangan VC1, VC2, VE1, VE2.

Jawab:

3. Untuk penguat cascode dari Gambar 4.143 tentukan :

a. Arus basis dan kolektor dari masing-masing transistor

b. Tegangan VB1, VB2, VE1, VC1, VE2, dan VC2

6. Soal Pilihan Ganda [kembali]

1. Gain arus sebuah transistor ditetapkan sebagai rasio arus kolektor terhadap :

a. Arus basis

b. Arus catu

c. Arus emitter

d. Arus Kolektor

Jawaban : a

2. Untuk bias emiter, tegangan pada resistor emiter sama dengan tegangan antara emiter dan :

a. Basis

b. Kolektor

c. Emiter

d. Ground

Jawaban : d

3. Pada bias pembagi tegangan, harus menggunakan :

a. Penyedia daya negatif

b. Resistor

c. Penyedia daya positif

d. Ground

Jawaban : b

7. Rangkaian Proteus [kembali]

Gambar Rangkaian 1 (4.64)

Gambar Rangkaian 2 (4.65)

Gambar Rangkaian 3 (4.66)

Gambar Rangkaian 4 (4.67)

Gambar Rangkaian 5 (4.68)

Gambar Rangkaian 6 (4.69)

Gambar Rangkaian 7 (4.70)

Gambar Rangkaian 8 (4.71)

Gambar Rangkaian 9 (4.72)

Gambar Rangkaian 10 (4.73)

8. Video [kembali]

9. Download File [kembali]

[menuju awal]